Двоичнодесятичный счетчик построеный методом управляемого сброса.

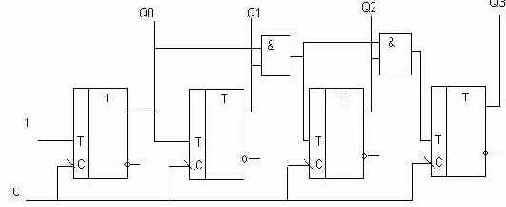

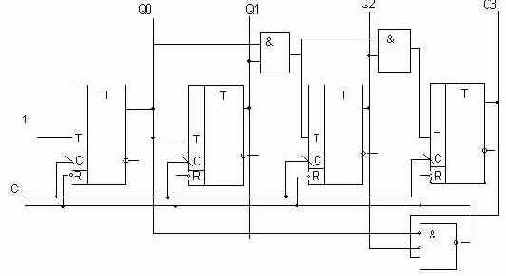

Построим на основе счетчика со сквозным переносом.

Со сквозным переносом двоичный

Метод управляемого сброса, заключается в формировании активного логического уровня при установлении на выходах счетчика кода соответствующего требуемому модулю счета и подачи от этого активного уровня на вход сброса асинхронной установки триггера, для обнуления разрядных схем счетчика. Активный уровень формируется на дополнительном логическом элементе И при поступлении на его входы требуемого кода. Например в двоично-десятичном счетчике соотв. код 1010 на выходах разрядных схем. Следовательно по приходе следующего кода 1010 должны быть установлены в нулевое состояние. Данный код поступая на вход логического элемента И-Не формирует уровень логического нуля на выходе что является активным логическим уровнем для инверсного входа R триггеров.

При использовании метода управляемого сброса, по импульсу при котором счетчик обнуляется на выходах триггеров формируется лишнее состояние(соответствующее коду обнуления) Если по условию работы счетчика формирование лишнего состояния недопустимо(даже кратковременное),то обнуление нужно проводить по последнему коду соответствующему модулю счета. Диаграммы импульсов двоично-десятичного счетчика реализующего метод управляемого сброса.

Если требуется получить выходной код в десятичной системе счисления то выходные сигналы с триггеров разрядных схем подключаются ко входу дешифратора.

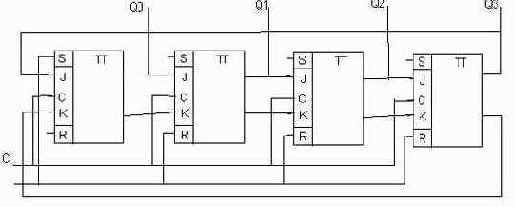

Кольцевой счетчик используется для замены дешифратора, при необходимости осуществления подключения какого либо сигнала с выхода устройства к определенному входу.

График!

Делители частоты импульсной последовательности.

Устройства последовательностного типа которое при подачи на его входы периодической последовательности импульсов, формирует на выходе такую же последовательность импульсов но с частотой повторения сигналов в несколько раз меньше чем входная. В делителе частоты последовательности импульсов может быть произвольной, последовательность кодов, характеризующих последовательность импульсов в отличии от счетчика, где последовательность импульсов(бит-кода), определяет количество импульсов, поступивших на вход счетчика.

Так как последовательность импульсов делителей частоты может быть произвольной, то она выбирается из соображений обеспечения пи заданном цикле наибольшей простоты меж регирстровых связей. Счетчик может выполнять роль делителя частоты, но пи большом числе разрядных схем это экономически не целесообразно. Частота следования импульсов на выходе в 2 раза меньше чем на входе. Если последовательно соединить несколько делителей частоты, то на выходе первого частота импульсов будет в 2 раза реже второго, на выходе второго делителя частота будет в 2 раза реже чем на входе, на выходе 3 на выходе в 2 раза реже.

Делитель частоты с коэффициентом деления 3.

Счетчик с периодом цикла n=3 имеет простейшие меж разрядные связи и может служить делителем частоты с коэффициентом n=5.

В тех случаях коэффициент деления не является простым числом он может быть представлен в виде сомножеств коэффициентов деления с простым числом. Напрмер n=6 2*3/

Таким образом схемы соединяются последовательно образуя требуемый коэффициент деления.

Запоминающие устройства – это узлы вычислительного устройства для хранения информации.